半導体の微細化を支える前工程|素子形成工程の最前線

カテゴリーblog

はじめに

半導体の高性能化・低消費電力化を実現するカギは「微細化」です。その微細化を支えているのが、シリコンウェーハ上にトランジスタや配線を形成する「前工程」の中でも特に重要な 素子形成工程 です。本記事では、半導体微細化を可能にする素子形成工程の概要と、その進化について解説します。

1. 素子形成工程とは

素子形成工程とは、半導体の基盤となるシリコンウェーハ上に、トランジスタやダイオードなどの基本素子を作り込むプロセスを指します。ここで形成される素子のサイズと精度が、半導体チップ全体の性能を大きく左右します。

2. 主なプロセスの流れ

素子形成には複数の精密な工程が組み合わさっています。

- 酸化:ウェーハ表面にシリコン酸化膜を形成し、絶縁層として活用。

- イオン注入:不純物を打ち込み、n型やp型の特性を持たせる。

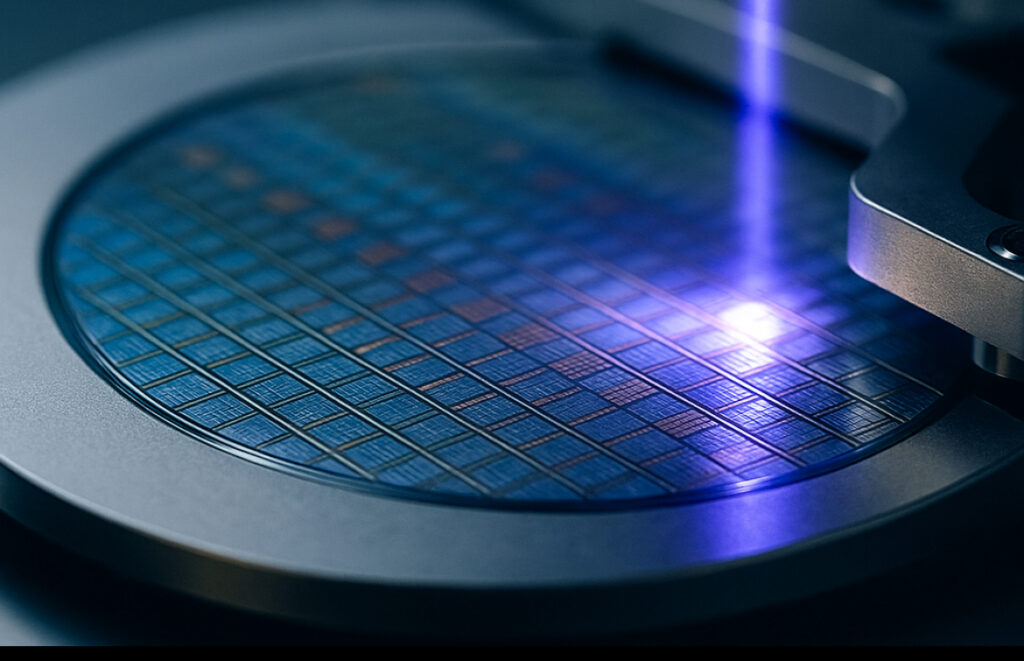

- フォトリソグラフィ:感光材(レジスト)を塗布し、紫外線で回路パターンを転写。

- エッチング:不要部分を除去し、微細な構造を形成。

- 成膜(CVD、PVD):絶縁膜や導電膜を堆積して層を重ねる。

これらを数十回繰り返すことで、ナノメートル単位の素子構造が積み上げられていきます。

3. 微細化を可能にする技術革新

素子形成工程における最大のブレークスルーは「露光技術」の進化です。

- DUV(Deep UV):193nmの波長を用いた従来技術。

- EUV(Extreme UV):13.5nmの極端紫外線を利用し、7nm以下の回路形成を実現。

さらに、トランジスタ構造も プレーナ型 → FinFET → GAA(Gate-All-Around) と進化し、より微細で高性能な素子形成を可能にしています。

4. 今後の展望

素子形成工程は、微細化の限界に挑戦し続ける領域です。物理的限界を補うために、3D実装技術や新材料(SiC、GaN)の採用も進んでおり、次世代の半導体は「微細化 × 新構造 × 新素材」の融合によって進化していくと予想されます。

まとめ

半導体の微細化を支える前工程、その中でも素子形成工程は、最も重要な核となるプロセスです。ナノレベルの世界で繰り広げられる精密加工こそが、現代の電子機器を支える原動力であり、今後の半導体産業の競争力を決める鍵となるでしょう。